3月17日直播丨CANN全链路算子开发体验提升

写代码:NDDMA + SIMD/SIMT 同构,让搬运、转置、Pad 只需要一个接口调用实现。跑算子:KernelLaunch 调度行为可控制,算子启动头开销降低到百纳米。找瓶颈:10 kHz 全维度 Profiling 与代码打点,使定位从“天”缩短到“秒”。Ascend 950 已为您搭建了一条从算子概念 → 代码实现 → 性能调优 → 业务落地的无缝通道。今天就加入 CANN 生态,体验算

AI 正以前所未有的速度渗透千行百业,模型规模、推理并发与多模态交互需求持续指数级增长。算子研发作为模型落地的核心环节,其编程体验、运行效率、调优,直接决定业务迭代速度与研发成本。

在此背景下,昇腾全新推出 Ascend 950 PR / Ascend 950 DT 两款 AI 芯片,围绕算子全链路关键环节实现多项技术突破:

NDDMA 多维搬运:一行 API 即可完成转置、广播、切片与多轴填充,代码从数十行压缩至 2–3 行。

CV 直连通路:新增 UB↔L1、L0C↔UB 直通通路,消除 GM 中转,实现向量, 张量融合算子“一跳”完成数据流转。

KernelLaunch 优化:优化核间同步,将算子启动开销从上一代的 3 µs 降至约 150 ns,调度延迟缩短至亚微秒量级,极大提升大模型推理与训练的迭代效率。

网络级 & 算子级 Profiling 增强:采样频率提升至 10 kHz,新增 Pipe Bubble、SIMT Stall、CCU Exec、L2 Sector Hit 等九大可视化维度,并提供代码打点自动关联,实现从“天”级定位瓶颈到“秒”级快速定位。

Ascend 950 PR/DT 新增特性,紧扣算子开发全流程关键环节 ——编程、运行、调优,在搬运算子、CV 融合算子编写、算子运行调度,以及整网与算子性能调优等场景,均实现了显著的体验优化与效率提升。

1. 算子编程易用性提升

NDDMA多维循环搬运

上一代芯片中,把二维矩阵从全局存储搬到局部 UB,通常需要手动计算每维步长、偏移量,编写两层甚至三层循环,代码量常在 30–40 行。Ascend 950 引入 NDDMA 指令,只需调用一次 DataCopy,并在模板参数中声明源 / 目的地址、步长、循环大小与填充规则,硬件自动完成转置、广播、切片与多轴填充。代码行数从数十行精简到 2–3 行 。

![[图片]](https://i-blog.csdnimg.cn/img_convert/5ab7a7feb9da7966bf7c6f92f8c507f9.png)

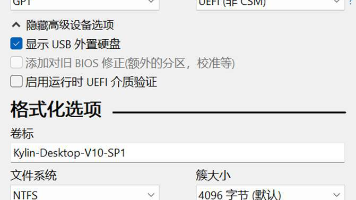

CV通路直连

上一代架构里,Cube(张量)与 Vector(向量)之间的数据必须经过全局存储(GM)中转,一次完整搬运要两次跨芯片读写,访存开销巨大。

Ascend 950 在芯片内部新增 UB↔L1、L0C↔UB 直连通路,并通过 Fixpipe 将结果直接送入 UB。融合算子(如 CV FA 合流)只需 “一跳” 即可完成数据流转,向量与张量高速直连、无缝协同,从根本解决传统 AI 芯片在融合算子计算中的瓶颈 。

![[图片]](https://i-blog.csdnimg.cn/img_convert/ddee9f1822e92c887265a8bdb8392227.png)

2. 运行时调度易用性提升

150 ns 超低启动

在旧版 CANN 中,对带有核间同步的算子调用 aclrtLaunchKernel填写参数时,需要额外插入同步地址,启动延迟通常在 3 µs 以上。Ascend 950 针对这样的算子进行了优化,无需额外插入同步地址参数,算子启动头开销降低到150 ns,约为旧版的二十分之一。对需要数百次循环的推理或微秒级训练循环来说,这一提升直接把调度开销压到可以忽略的层面。

可编程调度属性

通过 aclrtLaunchKernelCfg,开发者可以为每一次算子下发配置超时阈值(单位微秒),当算子执行时间超过设定值时,运行时返回超时错误,避免因算子卡死导致的整条流水线停滞;还可以开启 batch 调度模式,只有当所有目标核均空闲时才触发算子启动,确保全核同步算子能够在同一时间点完整执行,提升算子间的协调性。

Count Notify 的丰富计数模型

新引入的 Count Notify 支持三种计数方式:普通累加、位或和位与。配合四种等待条件(小于、等于、大于以及位掩码),可以轻松实现 1对N、N对1、广播、并发计数等复杂同步需求,仅需几行代码即可完成。

3. 调优 Profiling 易用性提升

采样频率提升至 10 kHz

上一代芯片 Profiling 每 10 ms 才采集一次数据,细粒度的流水线瓶颈根本不可见。Ascend 950将采样频率提升到每 0.1 ms 一次,实时捕捉硬件内部的每一次流水线切换、Cache Miss 与寄存器使用情况。

九大可视化维度

除了原来的 CCU Exec 与内存带宽外,新增了 Pipe Bubble(流水线空转)、SIMT‑Stall(线程级阻塞)、GPR Usage(寄存器占用)、L2 Sector Hit(128 B sector 命中率)以及每个 CCU 通道的带宽使用情况。用户在 MindStudio Insight 的 Timeline 中可以直接看到每一个维度的波形,快速定位是计算瓶颈还是访存瓶颈。

代码打点与自动关联

通过 AscendC::MarkStampImpl 在算子源码中插入打点,Timeline 上的每一次颜色块都能跳转回对应的代码行,省去手动对齐时间轴的繁琐。

CCU 打点

Ascend 950 首次向开发者公开 CCU(集合通信单元),并同步提供工具,支持开发者直接采集其执行耗时与通道带宽,使得在大模型的 All Reduce、All Gather 场景中,集合通信的真实开销一目了然。

SIMT 阻塞采样

针对包含分支与稀疏访问的 SIMT 算子,Profiling 能够统计 9 种阻塞状态的出现次数,帮助开发者快速找出导致流水线停滞的热点指令。

实际收益:在一次 2 GB 大模型推理测试中,原本 5% 的 CPU端瓶颈被定位为 SIMT Stall Branch,通过改写为 SIMD友好循环后,整体吞吐提升 2.3 倍,模型推理时间从 12 ms 降至 5.2 ms。

4. 结语——算子研发进入“一键全链路”时代

-

写代码:NDDMA + SIMD/SIMT 同构,让搬运、转置、Pad 只需要一个接口调用实现。

-

跑算子:KernelLaunch 调度行为可控制,算子启动头开销降低到百纳米。

-

找瓶颈:10 kHz 全维度 Profiling 与代码打点,使定位从“天”缩短到“秒”。

Ascend 950 已为您搭建了一条从 算子概念 → 代码实现 → 性能调优 → 业务落地 的无缝通道。今天就加入 CANN 生态,体验算子全链路高效开发,解锁AI 计算的核心竞争力。

B站直播预约链接: https://www.bilibili.com/opus/1180373977808240647?spm_id_from=333.1387.0.0

鲲鹏昇腾开发者社区是面向全社会开放的“联接全球计算开发者,聚合华为+生态”的社区,内容涵盖鲲鹏、昇腾资源,帮助开发者快速获取所需的知识、经验、软件、工具、算力,支撑开发者易学、好用、成功,成为核心开发者。

更多推荐

已为社区贡献95条内容

已为社区贡献95条内容

所有评论(0)