一文读懂Bumping的核心技术和种类0P1M, 2P2M是什么意思

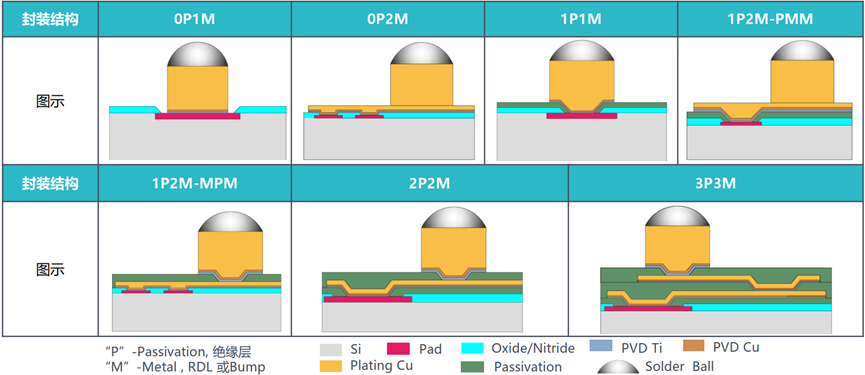

Bumping封装技术是高性能计算芯片的关键设计要素,通过七种不同结构(0P1M至3P3M)实现从简单到复杂的硬件设计路径。0P和1P结构适用于低端芯片,2P2M是高端CPU/GPU的主流选择,通过分层设计优化电源分配和信号完整性。3P3M结构代表前沿技术,采用三层基板实现极致性能,已被NVIDIA H100等产品采用。随着摩尔定律逼近极限,Bumping结构选择成为提升芯片性能的关键,不同层级结

在高性能计算芯片如CPU和GPU的封装设计中,Bumping凸块技术是实现先进封装的核心环节之一,Bumping封装技术已成为现代高性能计算芯片的关键设计要素,通过七种不同Bumping 封装结构(0P1M、0P2M、1P1M、1P2M-PMM、1P2M-MPM、2P2M、3P3M)实现了从简单到复杂的硬件设计路径。搭配基板层数和金属布线层数(Metal Layers)的组合,直接影响芯片的电气性能、热管理、信号完整性和成本控制。

更重要的是,随着摩尔定律逼近物理极限,先进封装技术正成为提升芯片性能与功能的关键路径,而Bumping结构的选择直接决定了芯片性能的关键。

关键术语

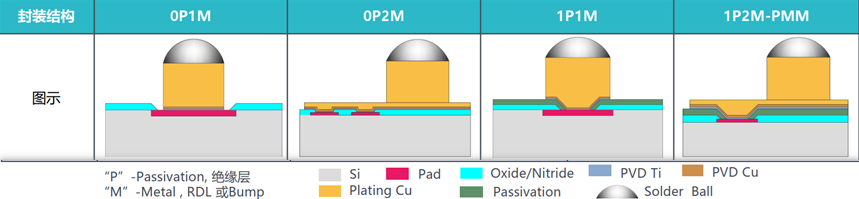

P(Passivation):基板的物理层数,通常指封装中独立基板的数量(如2P2M表示两块基板)。

M(Metal Layer):每块基板中用于布线的金属层数量。

PMM/MPM:金属层与钝化层(Passivation)的排列顺序(PMM = Passivation-Metal-Metal,MPM = Metal-Passivation-Metal)。

一、Bumping封装结构的基本原理与分类

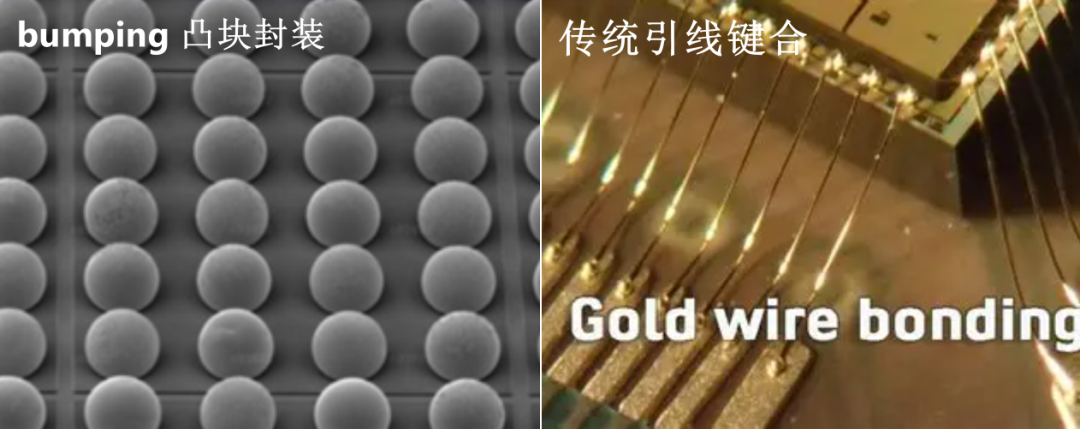

Bumping凸块封装技术是一种在芯片表面形成金属凸点的工艺,替代了传统的引线键合方式。这些凸点作为电气连接的中介,将芯片与封装基板或电路板上的焊盘连接起来。Bumping技术的核心优势在于缩短了电气连接路径,降低了信号损耗,同时提高了I/O密度和封装效率。

0P1M和0P2M结构代表无独立基板,直接在芯片表面形成凸点。其中,0P1M表示芯片表面仅有一层金属布线,而0P2M则包含两层金属布线。这两种结构通常依赖于芯片内部的RDL(重布线层)和钝化层,适用于低端芯片设计。

1P系列结构包含一个独立基板。1P1M表示单层基板+单层金属布线,1P2M-PMM和1P2M-MPM则表示单层基板+双层金属布线,但金属层与钝化层Passivation的排列顺序不同。PMM结构为钝化层→金属层→金属层,而MPM结构为金属层→钝化层→金属层。这种排列顺序的差异对信号完整性和电源分配网络有显著影响,MPM结构通过中间钝化层提供更好的电气隔离,适合高频信号传输。

2P2M和3P3M结构代表多层基板堆叠。2P2M表示两块基板叠加,每块基板包含两层金属布线;3P3M则为三块基板叠加,每块基板包含三层金属布线。这些结构通常结合TSV(硅通孔)和中介层(Interposer)技术,实现更复杂的电源分配网络和信号路由,适用于高端CPU/GPU和AI加速器设计。

0P和1P结构芯片级封装的硬件设计特点

0P1M和0P2M结构代表无独立基板,直接在芯片表面形成凸点的封装方式。这两种结构主要依赖于芯片内部的RDL和钝化层,适用于低密度、低成本的芯片设计。

在硬件设计上,0P1M结构通常在芯片表面形成一层金属布线,直接连接到凸点。由于缺乏独立基板,其电源分配网络(PDN)设计受到限制,主要依靠芯片内部的电源网络。这种结构的信号完整性较差,因为信号路径较长,容易受到干扰,不适合高频信号传输。电源层与地层之间的间距较大,导致电源阻抗较高,难以满足高性能计算芯片的电源需求。

0P2M结构在芯片表面形成两层金属布线,中间可能通过钝化层隔离。这种结构提供了更高的I/O密度和更复杂的布线能力,但仍受限于芯片尺寸和内部布线资源。在电源分配网络设计上,0P2M结构可通过分层布线实现一定的电源隔离,但整体电源阻抗仍高于多层基板结构。信号完整性方面,双层金属布线可减少部分干扰,但缺乏外部基板的屏蔽作用,高频信号性能受限。

0P结构的热管理主要依赖于芯片背面的散热设计,如散热片或均热板。由于缺乏基板的散热路径,热传导效率较低,不适合高功耗芯片。在硬件设计上,0P结构通常用于移动设备SoC、低端MCU和简单逻辑IC,如智能手机处理器和物联网设备芯片。这些应用场景对成本敏感,且功耗和性能需求相对较低。

1P1M、1P2M-PMM和1P2M-MPM结构代表单层基板的封装方式。这些结构通过增加独立基板,提高了I/O密度和信号完整性,但仍受限于单层基板的布线资源。

1P1M结构包含一个独立基板和一层金属布线。在硬件设计上,基板提供额外的布线空间和屏蔽作用,但单层金属布线难以满足高性能计算芯片的复杂互连需求。电源分配网络设计受限,难以实现低阻抗电源路径。信号完整性方面,单层布线易受干扰,高频信号质量下降。热管理上,单层基板散热能力有限,主要依赖于基板与散热片的连接。

1P2M-PMM结构包含一个独立基板和双层金属布线,采用PMM(钝化层-金属层-金属层)排列顺序。在电源分配网络设计上,PMM结构允许在底层金属层形成电源平面,上层金属层用于信号路由,从而实现一定的电源隔离。信号完整性方面,双层金属布线减少了部分干扰,但钝化层位于金属层下方可能导致层间寄生电容增加,影响高频信号性能。热管理上,单层基板仍存在散热瓶颈,但通过基板材料选择(如高导热性材料)可部分缓解。

1P2M-MPM结构同样包含一个独立基板和双层金属布线,但采用MPM(金属层-钝化层-金属层)排列顺序。这种结构在信号完整性方面具有显著优势,中间钝化层提供了更好的金属层间绝缘,减少串扰,特别适合高频信号传输。电源分配网络设计上,MPM结构允许在底层金属层形成电源平面,上层金属层用于信号路由,但电源与地层间距仍较大,难以实现最佳电源阻抗。热管理上,单层基板限制了热传导路径,但可通过基板与芯片之间的热界面材料(TIM)优化散热。

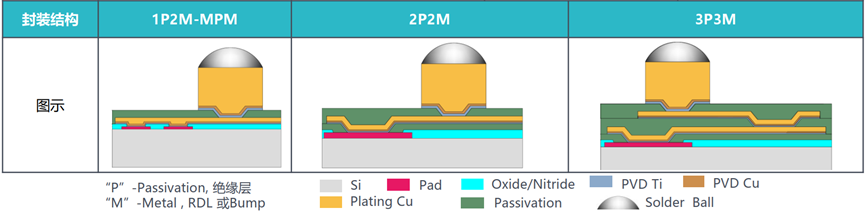

1P结构在CPU/GPU设计中的应用相对有限,主要出现在中低端产品线。例如,某些中端GPU可能采用1P2M-MPM结构,通过中间钝化层隔离高频信号通道,提升图形处理性能。在AI加速器和射频芯片领域,1P2M-MPM结构因其良好的信号隔离性能而更受欢迎。然而,随着高性能计算需求的增长,1P结构正逐步被2P2M和3P3M结构取代。

二、2P3P结构基板的硬件设计优化

2P2M结构包含两个独立基板,每块基板包含两层金属布线。这种结构通过基板堆叠,显著提高了I/O密度和互连复杂度,是当前高端CPU/GPU的主流封装选择。

在硬件设计上,2P2M结构通常采用分层设计策略:顶层基板专用于信号路由,底层基板专用于电源分配和地平面。这种分层设计优化了电源分配网络,降低了电源阻抗。根据电源完整性原理,电源平面与地平面应尽量靠近,而2P2M结构允许在底层基板形成完整的电源平面,顶层基板形成信号平面,从而实现最佳的PDN设计。

信号完整性方面,2P2M结构通过双层基板提供了更多的布线资源和更好的信号隔离。顶层基板可专用于高频信号路由,如PCIe通道和GPU核心间互连,而底层基板则专注于电源分配和低频信号。这种分层设计减少了信号间的串扰,提高了整体信号质量。此外,双层基板可通过调整金属层厚度和介电常数(如使用低k材料)实现50Ω或100Ω的阻抗匹配,满足高速数字电路设计需求。

热管理上,2P2M结构通过多层基板增加了散热路径。底层基板可直接连接散热片或均热板,而顶层基板则通过基板间的热传导材料实现散热。这种堆叠结构有助于分散热源,提高整体散热效率,特别适合高功耗CPU/GPU设计。

电源分配网络(PDN)设计是2P2M结构的核心优势。根据电源分配网络原理,Z0=√(L/C),其中D为电源平面同地平面之间的间距。在2P2M结构中,电源平面与地平面可紧密相邻,显著降低了电源阻抗。同时,去耦电容可分布在不同基板层,优化了高频电源响应。这种分层PDN设计在AMD EPYC 9004和Intel某些处理器中得到广泛应用,通过顶层基板专用于电源层,底层基板专用于信号层,实现了高效的电源分配。

三层基板的硬件设计突破

3P3M结构包含三个独立基板,每块基板包含三层金属布线。这种结构代表了当前先进封装的前沿技术,通过基板堆叠和金属布线分层,实现了极致的电源分配网络和信号完整性。

在硬件设计上,3P3M结构采用更精细的分层策略。顶层基板专用于高频信号路由和电源分配,中间层基板用于信号隔离和地平面,底层基板则专注于电源分配和散热。这种三层分层设计允许在电源与地层之间形成更薄的介质层,显著降低了电源阻抗,优化了高频电源响应。同时,信号层可紧邻地层,减少了信号路径长度和干扰,提高了整体信号质量。

电源分配网络(PDN)是3P3M结构的核心优势。根据电源完整性分析,V(ƒ)=I(ƒ)*Z(ƒ),其中Z(ƒ)为电源分配网络的阻抗函数。在3P3M结构中,多层金属布线允许设计专用电源层和去耦电容集成,降低了IR drop和噪声。这种结构通常在顶层基板设计为电源层,中间层基板为地层,底层基板为信号层,形成最佳的电源回路。此外,去耦电容可分布在不同基板层,优化了高频电源响应,满足GPU和AI加速器的高功耗需求。

信号完整性方面,3P3M结构通过三层金属布线提供了更多的布线资源和更好的信号隔离。高频信号(如HBM通道和PCIe通道)可专用于顶层基板,而低频信号则分布在底层基板,中间层基板作为地平面,提供了最佳的信号隔离。这种分层设计减少了信号间的串扰,提高了整体信号质量。同时,阻抗匹配可通过调整金属层厚度和介电常数实现,满足高速数字电路设计需求。

热管理上,3P3M结构通过三层基板堆叠增加了散热路径。底层基板可直接连接散热片或均热板,而顶层和中间层基板则通过基板间的热传导材料实现散热。这种堆叠结构有助于分散热源,提高整体散热效率,特别适合高功耗AI加速器和数据中心GPU。此外,基板材料选择(如高导热性材料)和底部填充(Underfill)技术可进一步优化热传导路径,减少热膨胀差异导致的机械应力。

在实际应用中,3P3M结构已被NVIDIA H100 GPU和台积电SoIC-P技术采用。通过3P3M结构实现了与HBM3存储器的3D堆叠,支持80GB HBM3和3TB/s带宽。台积电SoIC-P技术则通过三层基板堆叠,实现了更小的芯片尺寸和更高的封装密度,为系统级整合提供了理想平台。

鲲鹏昇腾开发者社区是面向全社会开放的“联接全球计算开发者,聚合华为+生态”的社区,内容涵盖鲲鹏、昇腾资源,帮助开发者快速获取所需的知识、经验、软件、工具、算力,支撑开发者易学、好用、成功,成为核心开发者。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)