FOCoS封装中UCIe Channel的SI分析

近年来,对人工智能(AI)、物联网(IoT)、超五代(B5G)及六代(6G)移动网络,乃至自动驾驶应用的需求大幅增长。在为高带宽需求设计多芯片时,FOCoS等先进封装技术是高性能计算产品的理想选择。最近推出的通信协议UCIe是一种芯片到芯片互连技术,旨在解决现有芯片互连技术的瓶颈,提高芯片间的通信效率和速度。UCIe定义了UCIe标准版(UCIe-S)和UCIe高级版(UCIe-A)两种封装,其中

·

扫描二维码

获取更多精彩

芯片SIPI设计

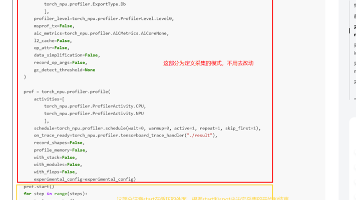

近年来,对人工智能(AI)、物联网(IoT)、超五代(B5G)及六代(6G)移动网络,乃至自动驾驶应用的需求大幅增长。这些系统都需要高速信号传输和高带宽并行总线来处理大量数据。传统封装方法已无法满足这些需求。在为高带宽需求设计多芯片时,FOCoS等先进封装技术是高性能计算产品的理想选择。最近推出的通信协议UCIe是一种芯片到芯片互连技术,旨在解决现有芯片互连技术的瓶颈,提高芯片间的通信效率和速度。UCIe定义了UCIe标准版(UCIe-S)和UCIe高级版(UCIe-A)两种封装,其中UCIe-A特别支持32位(x32)和64位(x64),传输速率高达32Gbps。下面将展示在FOCoS封装上,UCIe-A在32Gbps最高速率下满足x32和x64不同位配置的潜在设计,如图1所示。

鲲鹏昇腾开发者社区是面向全社会开放的“联接全球计算开发者,聚合华为+生态”的社区,内容涵盖鲲鹏、昇腾资源,帮助开发者快速获取所需的知识、经验、软件、工具、算力,支撑开发者易学、好用、成功,成为核心开发者。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)